### 行政院所屬各機關因公出國人員出國報告書 (出國類別:其他)

### 赴美國 Washington DC 參加 IEEE EMC+SIPI 2017 國際研討會心得報告

服務機關:經濟部標準檢驗局

姓名職稱:陳滄洲技士

派赴國家:美國

出國期間:106年8月6日至8月13日

報告日期:106年10月27日

| 行政院研考會/省(市)研考會 |

|----------------|

| 編號欄            |

|                |

|                |

|                |

|                |

|                |

#### 摘要

由電機電子工程師學會電磁相容分會(IEEE EMC Society)所舉辦的國際電磁相容研討會(International Symposium on Electromagnetic Compatibility),係為目前世界上最大的電磁相容標準、量測技術、學術整合、以及產業交流的國際性舞台,常年於美國境內舉辦,去(2016)年特別移師到加拿大的首都渥太華舉行,今年的地點則選在美國之華盛頓特區 Gaylord National Resort & Convention Center(蓋洛德國家渡假及會議中心)。本次會議共蒐集了將近 200 篇頂尖論文、數個不同主題的研討會及課程、以及電磁相容技術的現場示範與解說。此外,因過去幾次研討會融入信號與電源完整性(SIPI,Signal and Power Integrity)等主題,深獲好評,會議也開闢相關的專題研討會,供與會的專家學者經驗分享及技術交流,因此,藉由參與研討會的第一手資訊蒐集,可為本局未來在智慧化產業中電磁相容標準、檢測與驗證技術上重要之參考。

| 且 | ,        | 錄                             | <u>頁次</u> |

|---|----------|-------------------------------|-----------|

|   |          |                               |           |

| 壹 | `        | 背景說明                          | 5         |

| 貢 | `        | 活動行程簡述                        | 5         |

| 參 | `        | 會議記要                          | 6         |

|   |          | -、 專題研討會(Workshop)······      | 8         |

|   | _        | 二、 專題演講(Keynote Presentation) | 16        |

|   | $\equiv$ | E、 進入大會決選之論文 ······           | 20        |

| 肆 | •        | 心得及建議                         | 42        |

| <u></u> 圖目錄                                                                  | 頁次           |

|------------------------------------------------------------------------------|--------------|

| 圖 1: 蓋洛德國家渡假及會議中心之外觀                                                         | <del>7</del> |

| 圖 2: 蓋洛德國家渡假及會議中心二樓研討會會場入口處                                                  | 7            |

| 圖 3: 研討會會場大廳之壁報展示論文                                                          |              |

| 圖 4:提出之直流偏壓板:(a)單一直流偏壓源路徑之電路;(b)實體照片                                         |              |

| 圖 5: LCD 面板結構之 CE 雜訊源·······                                                 | 11           |

| 圖 6:調整增加 LCD 電路 GCLK 之 Tr / Tf 改善 CE 的例證 ··································· | 12           |

| 圖 7:(a)介紹專題演講主講人之大會網頁;(b)Mr. Julius knapp演講現場                                | 易19          |

| 圖 8:分離式抗墊穿孔結構                                                                |              |

| 圖 9: 共用抗墊穿孔結構······                                                          | 21           |

| 圖 10:使用 4 埠 VNA 量測一條 UTP 纜線之非平衡離散參數量測配置                                      | 22           |

| 圖 11:使用 4 埠 VNA 量測兩條 UTP 纜線間外來遠端串擾(AFEXT)耦合                                  |              |

| 之非平衡離散參數量測配置                                                                 | 22           |

| 圖 12:非屏蔽單極天線之總輻射功率(TRP)模擬與實際量測之驗證結果                                          | 23           |

| 圖 13: Rogowski coil:(a)提供電流路徑之導體;(b)兩組線圈······                               |              |

| 圖 14: 具霍爾(HALL)元件之電流感應器                                                      |              |

| 圖 15: 所提出之等效電路模型                                                             | 26           |

| 圖 16: ESD 槍之全波數值模組 ····································                      | 26           |

| 圖 17:雙層 PCB 結構設計之頂部/底部視圖                                                     |              |

| 圖 18:圖 11 結構再加入額外共模抑制單元之頂部/底部視圖                                              |              |

| 圖 19:(a)一個插頭;(b)一個插座;(c)組合成揭露之高速連接器                                          |              |

| 圖 20:(a)習知技藝之連接器金屬接腳;(b)揭露之高速連接器金屬接腳                                         |              |

| 圖 21: 偵測及報告微控制器測試 IC 應力事件之流程圖·······                                         |              |

| 圖 22:於測試 IC 進行特性量測所揭露偵測器之測試配置·······                                         |              |

| 圖 23: 壓縮脈波量測 3m 距離之時域響應······                                                |              |

| 圖 24: 有/無壓縮脈波量測 3m 距離之兩支天線響應比較 ····································          |              |

| 圖 25: 跨於放電火花間隙之過電壓準位對於時間延遲的影響                                                | 35           |

| 圖 26:使用 F-65 夾具夾於 ESD 槍梢(藍色)及 ESD 槍接地帶部(紅色)                                  |              |

| 量測電流之比較 · · · · · · · · · · · · · · · · · · ·                                |              |

| 圖 27: 具有階梯 (step) 電壓源的等效 RLC 電路模型                                            | 37           |

| 圖 28:以揭露模型之測試板於相位節點模擬的電壓振鈴雜訊與實際量                                             | 2.5          |

| 測之比較                                                                         |              |

| 圖 29: ITS 研發的連續波 (CW) 頻道測深器                                                  | 39           |

| 圖 30:頻道測深器執行訊號處理之流程圖 ····································                    | 39           |

| 圖 31:以 180°混合耦合器為基礎的架構:(a)50Ω終端負載;(b)使用                                      | 41           |

| 虚擬 DUT 於反射消法 ····································                            |              |

| 圖 32:LCD 基頻雜訊之頻譜:(a)無運用反射消除法;(b)運用反射消除法····                                  |              |

| 圖 33:美國華盛頓特區杜勒斯國際機場(IAD)外觀······                                             | ••••42       |

#### 壹、 背景說明

近年來國際上出現許多熱門議題,舉凡物聯網、智慧電網、工業 4.0,這些未來可能的明星產業,無不脫離「智慧」兩字,而產業智慧化一般需要靠前端的感測器將物理現象轉換成電子信號,再由電子處理器進行運算、判斷及控制,進而實現智慧化的目的,因此未來對於電子控制系統的依賴性將越來越高。當中,電子系統或複合式系統之間的互通性(interoperability)與網路安全(cybersecurity)等因素影響著智慧產業的發展,是近年電機電子工程師學會(IEEE)舉辦研討會的重要討論項目與主題,也同時是國際電工委員會(IEC)在制定國際標準上的主要方向之一。

電磁相容(EMC)以減低產品電磁干擾和增加抗擾度為目標,確保電子元件與系統之間能彼此共存、提升穩定度及安全性,故在智慧產業上佔有舉足輕重的角色。本次參加的電機電子工程師學會電磁相容分會(IEEE EMC Society)所舉辦的國際電磁相容研討會,旨在協助工程師、專家學者最新技術之分享及討論電磁環境效應及電磁相容等議題,該分會是目前世界上最大的電磁相容標準、量測技術、學術整合、以及產業交流的組織,藉由參與研討會第一手的資訊蒐集,可為本局在智慧化產業中電磁相容標準、檢測與驗證技術上重要之參考。

#### 貳、 活動行程簡述

- 8月6日(星期日):臺灣搭機赴美國加州舊金山(SFO),轉機至華盛頓 特區。

- 8月7日(星期一): 飛抵華盛頓特區杜勒斯國際機場(IAD), 搭乘公共交通運輸工具(5A巴士、M地鐵、NH2巴士)到達 Gaylord National Resort & Convention Center (蓋洛德國家渡假及會議中心), 辦理報到手續及參加專業技術研討會及課程。

- 8月8日(星期二):參與專業技術研討會、專題演講以及現場展示。

- 8月9日(星期三):參與專業技術研討會、海報展示以及現場展示。

- 8月10日(星期四):參與專業技術研討會、頒獎以及現場展示。

- 8月11日(星期五):參加專業技術研討會及課程。

- 8月12-13日(星期

六-星期日): 搭乘公共交通運輸工具(NH2巴士、M地鐵、5A 巴士)到達杜勒斯國際機場(IAD), 搭機赴加州 洛杉磯(LAX), 轉機返抵國門。

#### 參、 會議記要

電機電子工程師學會國際電磁相容研討會除常年於美國舉辦外,也會定期由非美國地區舉辦,去(2016)年特別移師到加拿大首都渥太華舉行,大會主席 Mr. Michael F. Violette 也特別在大會手冊內及第二天專題演講前的致詞開場白中,對今(2017)年選在美國首都(華盛頓特區)的做了簡單扼要的介紹。回想先前 2000 年 8 月間曾於華盛頓特區舉辦過的電機電子工程師學會國際電磁相容研討會,當時地點選在華盛頓特區的 Hilton(希爾頓)飯店,由已卸任的 Mr. Bill Duff 擔任主席,當年關心的主題包含「Y2K(year two thousand) software bug」(千禧危機之千年蟲)問題,經過 17 年後再度榮幸回到現今的華盛頓特區,關心的主題已演進為滲透全球社會之各種電子器材,包括無線、醫療設備、sensing(感測)、connectivity(連結)…等通稱為 EMC 與訊號及電力整合性的研究趨勢。本次研討會的活動地點位於 Gaylord National Resort & Convention Center(蓋洛德國家渡假及會議中心)(圖 1 所示為蓋洛德國家渡假及會議中心之外觀,圖 2 為蓋洛德國家渡假及會議中心二樓研討會會場入口處),緊臨 Potomac River(波多馬克河)的河岸。

本次會議共蒐集將近 200 篇的頂尖論文、數個不同主題的研討會及課程、以及現場最新電磁相容技術的實機展示,會期第二天上午則安排服務於 美國 FCC (聯邦通訊委員會) OET (Office of Engineering and Technology,工程與科技處) Chief Engineer (總工程師) Mr. Julius Knapp 為此次大會帶來精彩的專題演講。此外,由於過去幾次研討會融入信

號與電源完整性等主題,深獲好評,本次會議亦同樣地開闢相關主題,供與 會的專家學者經驗分享與及技術交流。以下將分別介紹本次會議的專題研討 會(WORKSHOP)、專題演講(KEYNOTE PRESENTATION)以及進入大會決選的論文 (NOMINEES FOR BEST EMC/SIPI/STUDENT PAPERS)。

圖 1: 蓋洛德國家渡假及會議中心之外觀

圖 2: 蓋洛德國家渡假及會議中心二樓研討會會場入口處

#### 一、專題研討會(Workshop)

1.Measurement Technique for High Precision and Noise Sensitive ICs Using Multiple Output-Bias Board with Low Baseband Noise (運用具低基頻雜訊的多重輸出偏壓板提 供高精確度及受雜訊敏感性IC之量測技術)

Poster Session (研討會會場大廳之壁報展示論文,如圖 3)發表者:

Yin-Cheng Chang, National Chip Implementation

Center, National Applied Research Laboratories,

Hsinchu, Taiwan

#### 摘要:

本論文針對高精確度及受雜訊敏感性之量測提出1種具有9個分隔式不同輸出電壓之直流偏壓板。與實驗室電源供應器比較下,量測結果可證明基頻雜訊於20kHz時得到改善達到 30dB。CMOS內部的電壓控制振盪器(Voltage-Controlled Oscillator,VCO)被用於評析電路效能上供電雜訊之影響程度。在3kHz~10MHz頻率補償下之相雜訊量測方面,所提出的偏壓板與內建於直流電源之訊號源分析器(Signal Source Analyzer,SSA)達成協議,然而植基於典型電源供應器的量測結果直接顯示出預料中的明顯雜訊。因此,針對受雜訊敏感性積體電路之特性,提出具有多重偏壓的技術可提供有效且實用的解決方案。

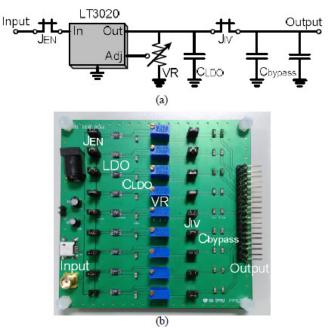

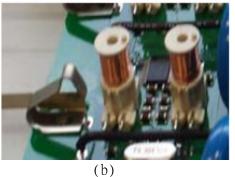

本篇提出其中一種直流偏壓板之設計,係由商用low-dropout(LDO) regulator(低壓差穩壓器,是線性直流穩壓器的一種,用途為提供穩定的直流電壓電源)IC構成,以利實現具有低雜訊之不同電源電壓的要求。LDO的主要優點在於產生的雜訊比起切換式(switching)DC-DC穩壓器來得低,適用於低雜訊、低電流、輸入與輸出電壓差很小的電路環境。據此,該LDO被用來調節來自電源供應器的輸出電壓,如圖 4(a)所示單一直流偏壓源路徑之電路,其中電路中設計LDO(以商用LT3020為例)由電源供給< 10V電壓,經設定可變電阻器(VR)以變動客製化的輸出電壓為 0.2V~9.5V,電容器  $C_{LDO}$ (電容值為2.2  $\mu$ F)用以維持該LDO的穩定性,

電容器  $C_{bypass}$  用以濾除路徑上之雜訊;圖 4(b)所示則為具有9條如上述相同之直流偏壓源路徑電路組成PCB元件布局(layout)的實體照片,該PCB板上電源輸入(Input)埠可設計迎合不同輸入來源之端子樣式,諸如DC jack(插孔)、micro-USB、SMA接頭或DuPont 2.54mm等連接器,此直流偏壓板由單一直流源輸入並能提供9種不同之穩壓輸出。經過量測頻段100Hz~10MHz間之驗證結果,所提出之直流偏壓板能有效降低電源基頻雜訊10dB以上,且在頻率10kHz以下基頻雜訊之改善效果尤其顯著。

圖 3:研討會會場大廳之壁報展示論文

圖 4:提出之直流偏壓板:(a)單一直流偏壓源 路徑之電路;(b)實體照片

# 2.Conducted Emission Reduction Technology for Liquid Crystal Display Devices (有關液晶顯示器裝置之傳導干擾降低技術)

Poster Session (研討會會場大廳之壁報展示論文)發表者:

Byunghee.Kim, EMC Part, Global Standards team, LG Display Co., Ltd., Gyeonggi-do, South Korea

#### 摘要:

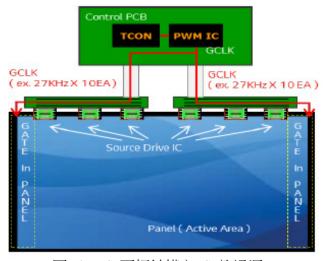

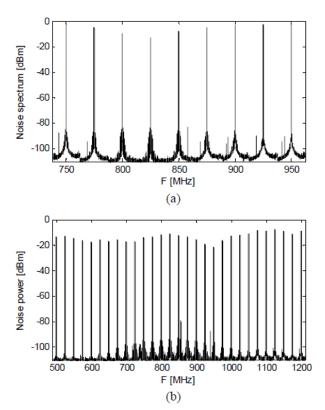

高解析度液晶顯示器(LCD)電視採用GIP(直接將閘極電路做進薄膜電晶體陣列(TFT Array)裡)技術以促成降低成本及外框窄化之設計。GIP是一種內建閘極(gate)驅動IC晶片的面板結構。GIP結構會增加電路電流及零組件,且影響傳導干擾變得較差。本篇論文提出有關具GIP的LCD電視其傳導干擾之分析及改善。傳導干擾的主要來源來自其中之GCLK(閘極時脈),GCLK會驅動具GIP的 LCD電視內部之閘極電路。從GCLK產生傳導干擾之雜訊來源與其波形有關。尤其會受到該波形的上升/下降時間及漣波的大小因素影響甚鉅。增加該波形的上升/下降時間將有助於減少傳導干

#### 擾之雜訊。

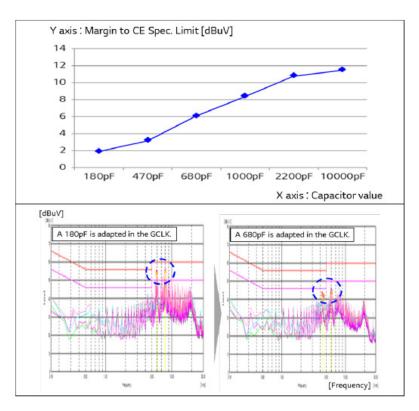

本研究分析 LCD面板結構之 CE雜訊源(如圖 5),LCD電路包含一個時序控制器(T-CON)單元及一個源極(Source)驅動IC,該 T-CON用以配合傳輸所接收到的影像資料至高速之數位訊號,而該源極驅動IC用以接收來自T-CON傳來的數位訊號,再分配其數位資料至面板的水平軸。同時,閘極(Gate)驅動IC則會驅動面板之源極驅動IC儲存的資料傳送到面板的垂直軸。圖 6所示以一個55吋 LCD面板的顯示器為其中實驗之例證,嘗試使用一個電容器(容值:108pF~10000pF)以調增 GCLK波形的 Tr(上升時間)/Tf(下降時間),可確實有效地降低 CE雜訊(其量測值與 CE限制值間之餘裕(margin)可達2dBuV以上~將近12dBuV),以圖中之電容器容值180pF與680pF為例,對於 GCLK Tr/Tf的影響結果,就有 4dbuV的餘裕差異量。

除此之外,另一個傳導干擾雜訊相關參數是驅動顯示器之峰值電流。當源極驅動器與閘極驅動器的輸出時間為同步時,峰值電流量將達到最大值。 所以,適當分配該源極驅動器與閘極驅動器的輸出時間將有效地降低傳導 干擾雜訊量。綜上所述,本篇之研究可瞭解 LCD產生的傳導干擾(CE)雜 訊,主要起因於驅動 IC之 GCLK的上升時間/下降時間及峰值電流,藉由 調整 LCD之 GCLK的 Tr/Tf及峰值電流以獲致 CE雜訊改善的明顯效果。

圖 5: LCD面板結構之 CE雜訊源

圖 6:調整增加 LCD電路 GCLK之 Tr / Tf改善 CE的例證

3.Debug and Analysis Considerations for Optimizing Signal Integrity in your Internet of Things Design (提供物聯網 (IoT)設計訊號整合最佳化之除錯及分析的考量)

主講者: Chris Armstrong, Rigol Technologies, Cleveland, Ohio, USA 摘要:

正值物聯網持續擴展應用範圍,包含家庭自動化、健身、影像顯示、追蹤 及傳統崁入式電子應用等例子,測試及最佳化設計之需求已成為明顯的事 實。正當物聯網擴展之際,這種測試需求已開始具體化成為一套幫助設計 團隊達到他們目標的發展能力。尤其特別重要的是產品越小,團隊及公司 越能多才多藝地規劃 IoT的路徑。當公司及工程師剛開始針對大規模設計 工作嘗試設計新樣式及成功的消費性商品時, IoT專案將持續且間歇地進 展,直到設計者發現每種標的應用方面獲得最理想形體及功能的組合為 止。太多焦點投注於形體上,原本就會產生如額外充電(加載)時間之可 靠性及惱人的問題。 首先我們考量測試需求作為評估上述問題之方法,一個設計團隊能夠加速商品市場化的時間,且最終地減少所需建立成功商品平台的重複流程。選擇手邊工作上最好的測試設備亦能促使工程師維持他們的起始預算需求。訊號整合是一種主要的設計觀點,由那些原本在IoT的輪廓擁有一半成功機會之態樣強調其重要性。將焦點專注於訊號整合,成為IoT應用之除錯到最終設計程序中最理想步驟的主要指標,如此將有助於使得一個小的IoT設計團隊得以影響他們的能力,且最終地回饋效能及舒適給他們的客戶端。我們在此將討論與IoT裝置有關訊號整合測試方法論的重要例證,以及他們如何將形體到功能的設計影響使用者(客戶端)之體驗。

#### 4. Reduction of EMC simulation efforts using Design of

Experiments(經由實驗之設計以減少電磁相容(EMC)模擬的嘗試)

主講者: Janne Hein, Chair of High-Frequency Engineering, Technical University of Munich in Cooperation with BMW AG, Munich, Germany

#### 摘要:

實驗之六標準差品質工具(six sigma(6σ) quality tool,用於流程改善的工具與程序)設計將被使用在EMC的模擬以支援電力雙動力汽車之預防性EMC驗證過程。DoE(Design of Experiments,實驗設計,屬於安排實驗和分析實驗數據的數理統計方法)為一種工具箱,使用於經由有效同時地改變所有輸入參數來確定所期待目標值上之多重輸入參數之影響。若把DoE方法應用在EMC模擬上,有助於EMC驗證過程中鑑定及分析產生影響之參數。車輛上之高壓系統的可靠性及保護逐漸受到重視,此等情形可由定義問題點之虛擬分析得到改善。DoE被應用來簡化及限定EMC模擬方面所定義之解決步驟,亦被應用於高壓系統具遮蔽纜線的例證。若能改善高壓纜線的遮蔽效果,則有利於提高汽車上的高壓系統並可符合整部車輛之電磁相容性。DoE結果顯示哪個參數會影響遮蔽的效果。因此,可挑選出哪些參數用作虛擬分析且不會影響結果,同時該等參數被挑選在參數範圍或甚至

群組內,成為模擬設計過程中的標準值以縮小其自由度。此預防性品質方法的使用(如 DoE)有助於大大地減少所需模擬耗費的嘗試,及改善模擬工程師日常的工作。

### 5.Measurement and Correlation of the PCB High Speed Links(PCB高速鏈結之量測暨關聯性)

主講者: Tao Wang, Brian Brecht, Roger Sinsheimer, Semiconductor Test Division, Teradyne, Agoura Hills, CA

#### 摘要:

針對PCB而言,具有高零組件密度之高速鏈結佈置設計必須滿足嚴格的機械 性及電子性規格要求。除了有關設計及製造流程變得困難以外,量測與模 擬之間的關聯性亦顯得極具挑戰性。

本篇論文著重於上述量測相關過程所遭遇的挑戰,且很少見於目前的學術文章有論述到上述高速鏈結問題(尤其是有關超過30Gbps傳輸速率之訊號而言)。我們將討論幾個重要因素,這些因素會影響模擬及量測相關過程的效果。本篇所討論之內容焦點在32Gbps的系統上,可提供一般高速鏈結發展的重要實用參考。

## 6.A Low Frequency Electric Field Probe for Near-Field Measurement in EMC Applications(EMC應用方面之近場量測所使用的一種低頻電場探棒)

主講者: Guanghua Li, David Pommerenke, Electromagnetic

Compatibility Laboratory, Missouri University of Science

and Technology, Rolla, MO, USA

#### 摘要:

設計一種具有高零敏度之低頻電場探棒,用以找出頻段 10 kHz~100 MHz 電子系統之輻射干擾來源。這種探棒包含探棒頂端的偶極天線 (dipole),內建運算放大器(op-amp)元件之儀表放大器,其輸出會透

過串接的RF放大器所放大。此探棒之偶極天線裝載著電容式的儀表放大器,會於低頻段產生高零敏度之平坦頻率效應。該儀表放大器亦可轉換差動(differential)偶極天線之輸出為單端訊號,而毋需內部混成(hybrid)訊號之處理。

除此以外,該儀表放大器亦可抑制探棒內偶極天線所引起之共模(common-mode)雜訊。從探棒之微帶線(microstrip trace)上面量測出的數據,顯示所需要耦合場的平坦頻率響應,以及無用(unwanted)耦合場於頻段 10 kHz to 100 MHz 間之 30 dB-40 dB 抑制量。

#### 7.The Future of Immunity Testing(耐受性測試之未來)

主講者: Flynn Lawrence, Applications Engineering, AR RF/Microwave Instrumentation, Souderton, PA, USA

#### 摘要:

在目前的電磁相容(EMC)測試領域中,尤指輻射耐受性(Radiated Immunity(RI))及傳導耐受性(Conducted Immunity(CI))測試,大多數使用於日常生活的消費性商品依據列檢之標準做測試,這些標準會要求單一掃描(swept)頻率聲調(tone)、透過寬頻等檢測方式。上述檢測方式已為大家接受之方法並行之多年,然而潛在威脅仍然一直不斷地發展存在著。

在現行之世界上,該潛在威脅可能涵蓋來自物聯網(Internet of Things(IoT))、通信、移動性(mobile)科技、自主性(autonomous)駕駛系統以及其他更多系統商品。那些訊號不被定義為一種單一聲調,而實際上被定義為複合性之寬頻波形。對於那些與上述潛在威脅共存之消費性商品而言,仍須勇於面對並應付曝露該等商品於所處環境之實際情況且尋求解決之道。

8.Site Contributions for Radiated Emission Measurement Uncertainties above 1 GHz(超過頻率1 GHz輻射干擾量測不確定性之場地貢獻度)

主講者: Zhong Chen, Zubiao Xiong, ETS-Lindgren, Inc., 1301 Arrow Point Drive, Cedar Park, Texas, 78613 USA

#### 摘要:

標準 CISPR 16-4-2 考量輻射量測結果之不確度評估方面的場地瑕疵提供指引。電波暗室(chamber)之場地電壓駐波比(Site Voltage Standing Wave Ratio(SVSWR))量測結果可被用來評估場地不確定性貢獻度之基礎。本篇論文有探討兩方面的不確定度評估,以及提出一種植基於 SVSWR 量測數據所估算不確定度之方法。首先,試論 SVSWR 量測結果係於使用目前之方法時,考量抽樣不足及量測數據暨分析報告不足等情況下,則 6 dB為電波暗室最大 SVSWR之假設是否有效的?再者,SVSWR量測時僅限於現行要求的轉盤(turntable)靜區(quiet zone)之前端、左側、右側及中心(center)(選擇性地)等位置。本篇論文研究這些量測位置的數據是否足以呈現整體靜區的特性。

#### 二、專題演講(Keynote Presentation)

摘要:本屆研討會邀請 Mr. Julius Knapp 主講(如圖 7), 主題為「在一個無線領域之世界中達到 EMC(電磁相容)的目標」(Achieving EMC In An Everything-Wireless World)。

Mr. Knapp 任職於 FCC 已有 42 個年頭,自 2006 年起擔任 FCC OET (Office of Engineering and Technology,工程與科技處)總工程師。 OET 長期提供 FCC 所需要科技工程專家意見的智庫來源及技術支援。OET 的任務為管理射頻頻譜並居於領導地位,以為美國人民建立競爭性科技及提供更多服務的機會。OET 制定並主管美國境內之頻率使用配置表,負責實驗證照制度及設備授權許可計畫,管制非認可(無執照)裝置的使用,從事工程及

技術方面之研究。

當無線存取設備的數量正以巨大步伐成長中,確保未來無線領域之世界中的電磁相容變得越來越具挑戰性,這些無線存取設備緊密地結合且僅依賴 微弱訊號之接收,與安全有關之大量應用被視為可靠的。由於某些科技及無線電射頻噪音來源之傳入引起意識性察覺干擾的興起,經由許多通訊產業反應在 FCC (美國聯邦通信委員會)科技諮詢會議而備受關切。本次演說將論及相關主題,諸如 FCC 目前發展的狀況、工業 EMC 標準及設備認可授權計畫暨其實施情形。全部的跡象在在地突顯出電磁相容的工作及從事電磁相容的成員逐漸擔負比過去較重要的角色。

Mr. Knapp 曾因為對於委員會傑出的服務獲頒 FCC 銀質及金質獎章,亦曾由於專業資深執行管理服務上的卓越成就被授予總統傑出獎。Mr. Knapp 曾因專業技術致力於公共服務的優秀表現得到 Eugene C. Bowler 獎、獲 FCBA(Federal Communications Bar Association,聯邦通訊律師協會)頒予政府服務獎、獲頒 WCAI(Wireless Communications Association's International,無線通訊協會之國際性組織)政府領導獎及獲頒聯邦通訊專業諮詢工程師協會 E. Noel Luddy 獎。

Mr. Knapp 身為 IEEE 的終身會員,曾在 1974 年取得紐約市立學院的電機工程學士學位。Mr. Kanpp 於本次 2017 EMC+SIPI 研討會中演講有關在一個無線領域之世界中達到 EMC(電磁相容)的目標。此演說內容提出未來無線領域挑戰且不斷擴充運用的概述,包含 5G(第五代行動通訊技術標準暨協定)、IoT(Internet of Things,物聯網)、連接的車輛、無人駕駛的航太系統、植基於動態頻譜存取之寬頻衛星服務及科技(其中以電視及市民寬頻無限電服務為例),並論及 FCC 目前發展的狀況、工業 EMC 標準及設備認可授權計畫暨其實施情形。

物聯網概念最初起源於比爾蓋茲在1995年《未來之路》這本書中的內容,國際電信聯盟(International Telecommunication Union(ITU))於 2005年正式提出物聯網概念,日本於2003年便開始進行無所不在網路

(Ubiquitous Network, UN)的研究計畫,美國總統歐巴馬於2008年提倡物聯網振興經濟戰略。類似物聯網的科技有無線感測網路(Wireless Sensor Network)及網路實體系統(Cyber Physical Systems, CPS),無線感測網路係由無線資料彙集器(Sink)與數個感測器(Sensor)所構成的網路系統,而CPS與無線感測網路的差異,在於CPS能依照不同事件的發生啟動相對應的指令及程序,透過聯網技術將智慧物件所提供的資訊,經由統一格式或標準的制定,使各個CPS系統間能夠互相溝通並傳遞分享之資訊,系統端所能參考與分析的資訊不再僅是針對單一事件做出處理。

物聯網可分為三個階層: 感知層(Device)、網路層(Connect)及應用層(Manage)。

- (一) 感知層:可分為感測技術與辨識技術,針對不同的場景進行感知 與監控,具有感測、辨識及通訊能力的設備。

- (二)網路層:包含各種不同通訊範圍與傳輸速率的無線通訊網路,依照是否直接連結上網際網路的方式,可區分為內部網路(稱區域網路)及外部網路(含電信網路及數據網路),將感知層收集到的資料傳輸至網際網路,建構無線通訊網路上分別運用「電信網路」(TeleCom)傳輸語音及「數據網路」(DataCom)傳輸資料,藉由異質網路閘道器整合多種不同之無線通訊協定使之彼此溝通,但異質網路的整合仍遇到 ISM(工科醫)頻寬不足及 IP 位置不夠充足等挑戰。

- (三)應用層:物聯網與行業間的專業進行技術融合,根據不同的需求開發出相應的應用軟體(例如:智慧電網(smart grid)之 AMI (Advanced Metering Infrastructure,智慧型電表基礎建設)及其架構下之智慧電表(Smart Meter))。

目前物聯網未來的發展與挑戰,包括:嚴加制定相關的感知標準,避免 物聯網資訊效率低落的情形;改善頻道的動態選擇性使得資料傳輸更具適應 性;物聯網的資料及設備資源仍待有效的整合配置及確保資訊安全之管理。 時至今日,電磁相容議題牽涉到的不再只是單一面向甚至必須考慮到特殊的環境,因此,在相同頻寬下多系統的共存(co-existence)和互通性(interoperability)問題,以及有意圖(intentional)與非意圖(unintentional)的電磁干擾等複合式問題驅使著許多軟硬體、系統工程師重新思考電磁相容所扮演的重要且關鍵性定位,其範圍不僅僅涵蓋一般大眾所觸及的智慧手機、智慧家電、智慧車、無人機甚至牽涉到金融、IoT(物聯網)、軍事、太空等領域,Mr. Julius Knapp 最後指出,隨著處理器時脈的增加以及電路體積的縮小,未來將持續面臨信號完整性、電源完整性以及電磁相容的挑戰。

圖 7:(a)介紹專題演講主講人之大會網頁;(b)Mr. Julius knapp演講現場

#### 三、進入大會決選之論文

1.Estimating the Via-Plane Capacitance for Differential Vias with Shared-Antipad Based on Analytical Equations (依據解分析方程式評估具有共用分擔抗墊之差動穿孔的穿孔平面電容)

作者群:(1) Ying Zhang, Missouri S&T EMC Laboratory, Missouri University of Science and Technology, Rolla, MO. 65401, USA

(2) Chunchun sui, Cisco Systems, Inc., San Jose, CA. 95134, USA

#### 摘要:

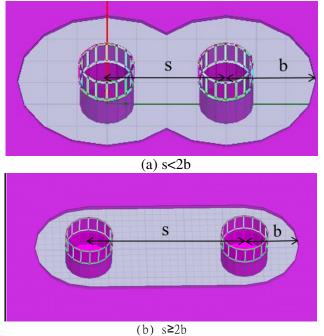

共用抗墊(用以提供PCB每一電源層及接地層之圓形間距,防止與平面產生電氣短路)之穿孔結構通常被使用於高速印刷電路板(PCB)的設計。因此,此種幾何結構之穿孔平面電容的準確評估有助於促進工程設計,已顯現其重要性。在本篇論文中,藉由運用抗墊等同面積與比率修正之方法,分離式抗墊穿孔結構(圖 8)之穿孔平面電容解析方程式已被延伸應用於共用抗墊穿孔結構(圖 9)的例證。此提出的方法透過廣泛使用於高速 PCB 設計之典型結構且運用 HFSS(High Frequency Structural Simulator,高頻結構模擬器,屬於電磁結構的有限元素法解算器)的數值方法所驗證。

圖 8:分離式抗墊穿孔結構

圖 9:共用抗墊穿孔結構

2. In Situ Crosstalk Measurements of Long Cables - The Multi-Network Analyzer Method (長纜線之就地串擾量測 - 多重網路分析儀方法)

作者群: Chris J. Collins, Student Member, IEEE and Joey R. Bray,

Member, IEEE, Department of Electrical and Computer

Engineering, Royal Military College of Canada, Kingston,

ON, Canada

#### 摘要:

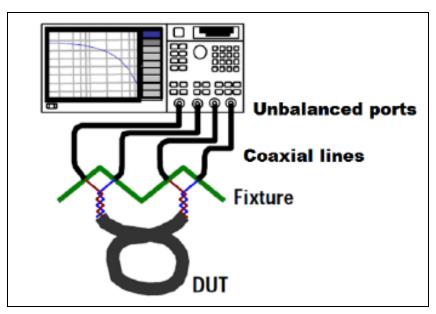

乙太網路之間的外來串擾(Alien Crosstalk(AXT))產生干擾且對於系統安全上造成潛在的威脅。由於儀器使用時在近端及遠端之需要,對於先前完成配置之部分進行AXT量測頗具挑戰性。雖然目前已有進行上述量測目的之商業型可攜式儀器可供使用,仍需使用平衡對不平衡阻抗匹配器(balun)提供乙太網路纜線上平衡與非平衡間阻抗匹配的訊號傳輸,但此會限制頻寬且衍生該balun不必要的響應。本篇論文提出毋需使用任何balun的一種新穎系統,此系統使用非平衡式網路分析儀,配置於連接纜線的兩端處。此非平衡式網路分析儀有同步及鎖相(phase locked)功

能,可使得產生的非平衡串擾(crosstalk)量測數據透過數學運算轉換至平衡及且共用的模式。在此針對多重網路分析儀(以圖 10及圖 11所示 4埠 VNA(向量網路分析儀)量測UTP纜線為例)提出一種新的校正方法並經過驗證,且使用該新穎系統進行最差情況(worst-case)串擾之量測亦同時被提出於此篇內容。

圖 10: 使用4埠VNA量測一條UTP纜線之非平衡離散參數量測配置

圖 11: 使用4埠VNA量測兩條UTP纜線間外來遠端串 擾(AFEXT)耦合之非平衡離散參數量測配置

### 3.Worst Case Prediction of Shielding Effectiveness of Board Level Shields (板層屏蔽效應最差狀況之降低)

作者群:(1) Ruijie He, Missouri University of Science and Technology Rolla, MO, USA

(2) Mohammad Ali Khorrami, Laird Tech, Randolph, MA, USA 摘要:

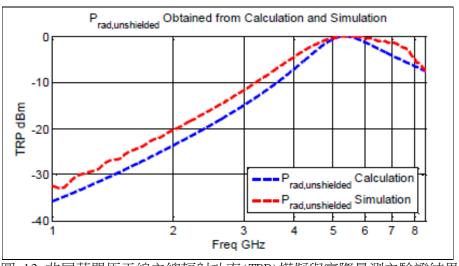

本篇論文提出一種方法用來預測板層屏蔽(BLS)最差狀況之屏蔽效應。 此方法用以評估板層屏蔽形成凹孔在低於或高於第一諧振頻率時屏蔽的屏蔽效應(SE)。板層屏蔽之孔徑被塑造視為具有已知輻射效率之天線。 該凹孔內之最大場強經過評估的結果,用來計算高於凹孔第一諧振頻率之 驅動天線的磁場電流。同樣地,藉使用此諧振時之IC電路模組,凹孔內之 場強低於第一諧振頻率時亦需要被評估。因此,一種估計均勻配置孔徑之 輻射功率的近似模擬公式在此被揭露,最差狀況之預測透過全波模擬得 到驗證且亦能應用於實際板層屏蔽的量測(以圖 12所示非屏蔽單極天線 之總輻射功率(TRP)模擬與實際量測之驗證結果為例,近似匹配)。

圖 12:非屏蔽單極天線之總輻射功率(TRP)模擬與實際量測之驗證結果

### 4.Conducted Interference on Smart Meters (智慧型電表之傳導干擾)

作者群:(1) Cees Keyer, University of Twente, Enschede, The

Netherlands

(2) Frank Leferink, Thales Netherlands, Hengelo, The

#### 摘要:

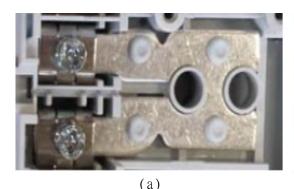

現代電子設備產生日益遞增之傳導干擾正使得電子或靜態電力表遭受更多的問題。當這些電表裝配通信鏈結時,被稱為智慧型電表,已正在取代傳統機電式電表的角色。目前已知的實例有關使用於太陽能光電系統之主動式饋入轉換器,產生的傳導電磁干擾會影響靜態電力表顯示較正常值低的讀值。在一個控制的環境中,三相電表曾被發現在第一時間顯示較正常值高的讀值。那些實驗係使用正弦波電壓流經一個四象限功率放大器所進行的。我們於實驗中觀察,量測的電力讀值增加到正常讀值的 +276%,也有量測到電力讀值減少為正常讀值的 -46%。我們發現,經由羅柯斯基線圈(Rogowski coil,如圖 13)電流感應器會量測到正向讀值,而植基於霍爾效應(Hall effect)元件之電流感應器(圖 14)卻會量測到負向偏差之讀值。上述實驗曾於實驗室所供應之標準及低內部阻抗主電源並連接很多電表等配置下,反覆多次進行驗證。目前我們已曾記錄的正向讀值達到+582%及負向讀值到 -32%。

圖 13: Rogowski coil: (a)提供電流路徑之導體;(b)兩組線圈

圖 14: 具霍爾(HALL)元件之電流感應器

5.Efficient Circuit and EM Model of Electrostatic

Discharge Generator (靜電放電產生器之有效電路及電磁(EM)

模組)

作者群:(1) Jawad Yousaf, Department of Electrical and Computer

Engineering, Sungkyunkwan, University Suwon,

Republic of Korea

(2) Jinsung Youn, Design Technology Team, Memory Division, Samsung Electronics Co. Ltd, Hwaseong, Republic of Korea

#### 摘要:

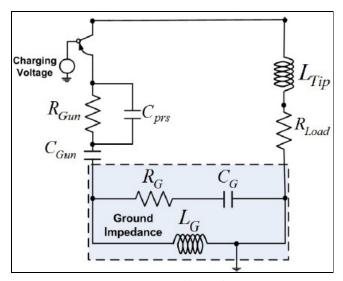

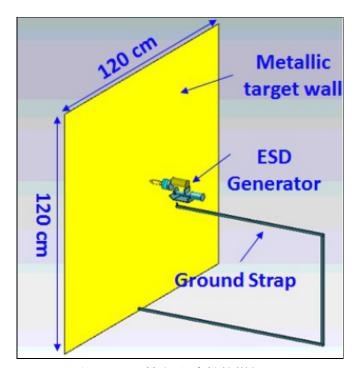

本篇論文提出一種技術,關於有效率的、簡易的及快速的等效電路(如圖 15),以及靜電放電(ESD)產生器的全波數值模組(如圖 16所示ESD槍 之全波數值模組)。在此,我們亦提出一種 NoiseKen(一家日本經營 EMC設備的公司)ESD模擬器(靜電槍)之新穎的電路模組,此乃植基於標準波形校正設定之頻域(frequency domain)量測。相同產生器之簡易全波電磁(EM)模組(具有較少的計算資源)配合使用商業 CST(一家研發與銷售高性能全頻域電磁模擬軟體公司,總部位於德國)MWS(一種提供高頻元件之 3D電磁(EM)模擬專家工具)軟體,亦同時被提出於本篇內容。本篇驗證之結果值得觀察的是,關於量測到的 ESD參考波形、電路模組以及產生器的3D模組等彼此間能夠獲得良好之一致性。

圖 15: 所提出之等效電路模型

圖 16: ESD槍之全波數值模組

6.Electrostatic Discharge Protection Device and Common Mode Suppression Circuit on Printed Circuit Board Codesign (印刷電路板共同設計之靜電放電保護裝置及共模抑制電路)

作者群:(1) Chin-Yi Lin, Graduate Institute of Communication

Engineering, National Taiwan University Taipei, Taiwan

(2) Tzong-Lin Wu, Graduate Institute of Communication Engineering, National Taiwan University, Taipei, Taiwan

#### 摘要:

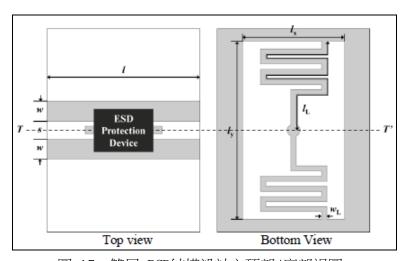

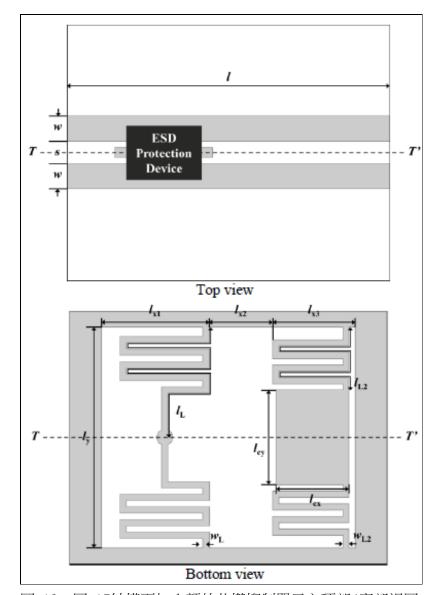

本篇論文介紹一種具有靜電放電(ESD)保護裝置及共模抑制電路在印刷電路板(PCB)上之共同設計,以利滿足高速輸入/輸出之介面需求。ESD保護裝置之特性及模組經過我們的研究後,將其應用至共模抑制電路的設計。

所提出的雙層 PCB結構設計(如圖 17所示 ESD保護裝置與共模抑制電路 共同設計於PCB上之結構)於頻段 2.22 GHz~ 2.76 GHz間進行共模雜訊 量測之結果,可抑制-10 dB;若上述的設計再加入額外共模抑制單元 (圖 18)後,從 2.25 GHz以上甚至超過 8GHz頻段進行量測,亦可強化 寬頻的雜訊抑制效果。而且,依本篇提出設計的電路與參考電路分別於實 驗結果看得出差動訊號之插入損耗是相似的。

圖 17: 雙層 PCB結構設計之頂部/底部視圖

圖 18: 圖 17結構再加入額外共模抑制單元之頂部/底部視圖

7.Design and Verification of a High-Speed Connector for Multi-Media System (多媒體系統所使用高速連接器之設計及驗證)

作者群:(1) Huijin Song, School of Electronic Engineering, Korea

Advanced institute of Science And Technology,

Daejeon, South Korea

(2) Junho Lee, Electric Connector Business Division,

Korea Electric Terminal Co., Ltd, Incheon, South

Korea

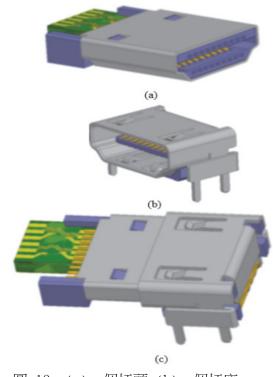

#### 摘要:

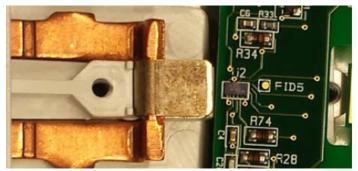

最近高解析度媒體裝置諸如 8K超高解析度(UHD)電視及虛擬實境(VR) 的數量正快速地增加中。這些多媒體系統需要較高的資料傳輸率才能應付 高解析度及多樣性功能等規格。有鑑於此技術趨勢的升高,高速率連接器 及纜線亦顯現其重要性。在本篇論文中,我們提出一種可傳輸高速媒體資 料的高速連接器,包括一個插頭及一個插座(圖 19)。所提出的連接器 係植基於時域反射率計(TDR)的量測結果設計出來的,此乃因為該 TDR 會顯示電磁(EM)波傳播。該連接器上的金屬接腳(pin)及短梢 (stub) 會經過修整以降低波反射,經修整變小的短梢亦能降低資料接腳 之間的耦合效應,且修整過的接腳可提供較均匀的特性阻抗(圖 20 (b)) 以避免訊號衰減,反觀習知技藝之連接器金屬接腳呈現不均勻形狀 及空間(圖 20 (a)),會產生訊號衰減。習知技藝的連接器僅著重於實 體的連接及機械上的可靠性。然而,一旦資料的傳輸率提高時,該連接器 的電氣效能也同樣變得非常的重要。因此,對於該高速連接器而言,有關 插入損耗、衰減(attenuation)對串擾(crosstalk)比(ACR)以及阻 抗不匹配等之信號整合(SI)分析變得不可或缺。3D電磁(EM)模擬工具 在此被使用來比對習知技藝的連接器與所揭露連接器,以驗證其間之差異 性。綜上所述,相較於習知技藝的連接器,所揭露之高速連接器確能提供 較良好的電氣效能。

圖 19: (a)一個插頭;(b)一個插座; (c)組合成揭露之高速連接器

圖 20: (a)習知技藝之連接器金屬接腳; (b)揭露之高速連接器金屬接腳

### 8. An On-Chip Detector of Transient Stress Events (一種偵測暫態應力的晶片上偵測器)

作者群:(1) A. Patnaik, Missouri University of Science and Technology, Rolla, MO, 65409

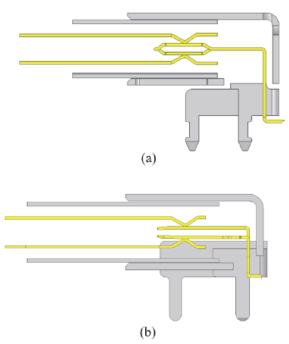

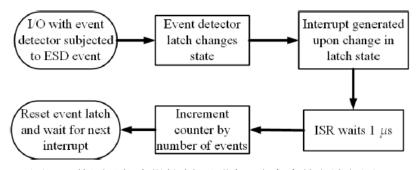

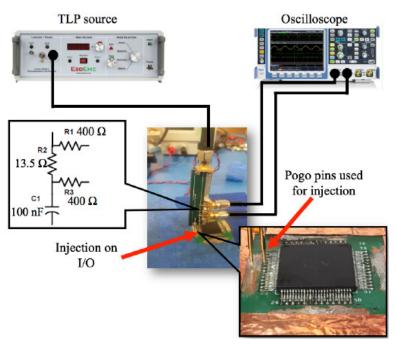

(2) J. Feddeler, NXP Semiconductors, Austin, TX, 78735 摘要:

對現今的電子系統而言,有關靜電放電(ESD)或電性快速暫態響應(EFT)相關議題之測試及除錯,正是深具挑戰性的工作。本篇論文提出一種晶片上電路的設計,針對輸入/輸出墊之 ESD保護結構,此電路供以值測及儲存快速暫態應力事件的發生情形。依圖 21所示一種流程圖,說明測試期間,微控制器軟體被使用於配合值測及報告微控制器測試IC應力事件之流程;所揭露值測器於測試IC進行特性量測配置(圖 22),搭配傳輸線脈波(TLP)的輸入並使用彈簧接腳(pogo-pin)探針注入暫態應力於輸入/輸出墊與VSS引腳之間。透過 90奈米科技之測試電路的量測及模擬驗證結果,證明此電路可準確地值測及記錄暫態應力事件的存在(以低至 0.9A峰值電流或短至 1奈米(nm)持續時間(duration)之值測能力),由此說明此值測器即便處於IC典型溫度及過程變化之際,仍可有效地執行其功能沒有問題。這種小尺寸的值測器將可有效地使用在甚至低成本的商業積體電路(IC)上。

圖 21: 偵測及報告微控制器測試IC應力事件之流程圖

圖 22: 於測試IC進行特性量測所揭露偵測器之測試配置

- 9.Free Space Antenna Factor Computation Using Time

Domain Gating and Deconvolution Filter for Site

Validation of Fully Anechoic Rooms (針對全電波暗室

(Anechoic Rooms)的場地驗證,使用時域門控(time domain gating)及反迴旋(deconvolution)濾波器計算自由空間的

天線因子)

- 作者群:(1) Anoop Adhyapak, ETS-Lindgren Inc., 1301 Arrow Point Drive, Cedar Park, TX, USA

- (2) Kazuo Shimada, ETS-Lindgren Japan Inc., 4-2-6 Kohinata, Bunkyo-hu, Tokyo, Japan

#### 摘要:

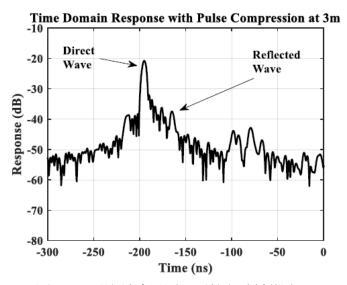

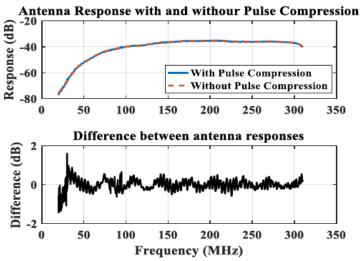

本篇論文提出一種替代方法,提供脈波壓縮時,使用時域轉換及反迴旋濾波器以計算自由空間的天線因子。反迴旋濾波器有助於壓縮時域脈波以利從反射波區分出直射波,亦有助於評估全電波暗室場地驗證時之自由空間天線因子。本篇論文中包含一對 ETS-Lindgren公司之天線(型號:3110C

及3180C),運用所揭露的方法使用反迴旋濾波器及韋納濾波器(Wiener filter)進行模擬實驗,分別以壓縮脈波量測 3m距離之時域響應為例 (圖 23),以及有壓縮脈波與無壓縮脈波量測 3m距離之兩支天線響應的比較為例(圖 24)。植基於上述模擬實驗之結果,我們瞭解所揭露的方法藉由這對天線的量測結果能被實現,且被使用於全電波暗室之場地驗證。自由空間之標準場地衰減(Normalized Site Attenuation)量測結果仍符合標準所規定 ±4 dB規格之要求。

圖 23: 壓縮脈波量測3m距離之時域響應

圖 24: 有/無壓縮脈波量測3m距離之兩支天線響應比較

- 10.Detection Methods for Secondary ESD Discharge During IEC 61000-4-2 Testing (IEC 61000-4-2(静電放電耐受性測 試標準)測試期間之二次靜電放電(ESD)偵測方法)

- 作者群:(1) Shubhankar Marathe, EMC Laboratory, Missouri

University of Science and Technology, Rolla, MO-65401, USA

- (2) Mike Hertz, Teledyne LeCroy, Chestnut Ridge, New York, USA

#### 摘要:

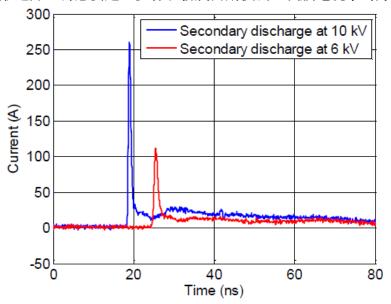

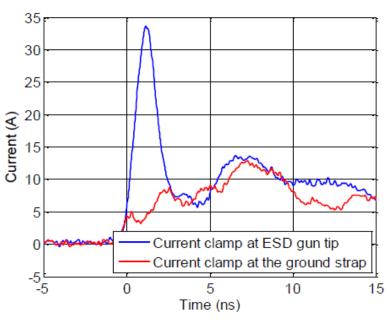

當靜電放電達到產品本體非接地之金屬部分時,該金屬部分相對於接地之 電壓將會增加。倘若對於接地的隔離不足夠時,則會產生二次靜電放電的 情形。鑑於二次靜電放電常常會引起系統的擾亂或損壞,且甚而至導致不 良性的重現結果,所以偵測二次靜電放電的發生是很重要的。如果使用示 波器監測放電電流,則測試儀器可能漏測到二次放電的波形。這是因為介 於一次與二次放電發生之間的時間延遲,會有奈秒(十億分一秒)~毫秒 (千分之一秒)的變化。這種延遲端視二次間隙之過電壓量、波形的形狀 (shape)及濕度等因素而有所變動。如圖 25所示跨於放電火花間隙之過 電壓準位對於時間延遲的影響,其中一次放電與二次放電之間的時間延遲 受到放電電壓設定、間隙長度、表面材料及濕度等影響,當放電電壓越高 時,二次放電的時間延遲就會越低。目前使用的示波器無提供此功能性可 供自動偵測二次放電現象。本論文研究的目標就是依據不同之量測設定以 分析不同類型的二次放電案例。這些量測數據會被分析有關參數的鑑定, 其中該參數可供作二次靜電放電之(低、假或漏失的)自動偵測。由於靜 電放電槍已為人知受到該槍內部繼電器(relay)的切換影響而產生前脈 波及後脈波情形,以致於很難區分二次放電與靜電放電槍之前脈波-及後 脈波現象。倘若使用F-65夾具夾於ESD槍梢,雖可量測到放電電流之高頻 部分,但需要考量連接纜線及探棒之負載效應影響放電電流波形的形狀;

若使用F-65夾具夾於ESD槍接地帶部時,雖可降低上述探棒之負載效應, 卻受到頻寬限制而不能正確地量測到原始峰值電流。如圖 26所示即為使 用F-65夾具夾於ESD槍梢(藍色)及ESD槍接地帶部(紅色)量測電流之比較。 因此,正值透過靜電放電槍梢(tip)或接地金屬帶部(strap)量測到放 電波形之際,有必要建立步驟以發展自動偵測二次放電現象的方法。

圖 25: 跨於放電火花間隙之過電壓準位對於時間延遲的影響

圖 26:使用F-65夾具夾於ESD槍梢(藍色)及ESD槍接地帶 部(紅色)量測電流之比較

- 11. Modeling and Analysis of Conductive Voltage Noise for a DC-DC Buck Converter (直流-直流降壓式轉換器之傳導電壓雜訊的模式及分析)

- 作者群:(1) Yanling Lu, Tsinghua Sichuan Energy Internet Research Institute

- (2) Jun Fan, Fellow, IEEE, University of Electronic Science and Technology of China

- (3) Tun Li, University of Missouri Science and Technology

#### 摘要:

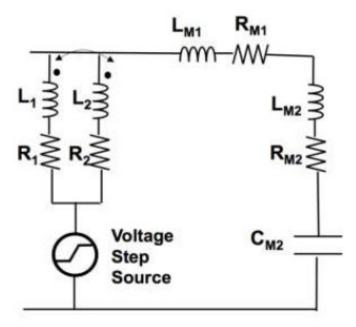

來自同步型降壓式轉換器的電壓雜訊已為人熟知會引起電子系統設計上的 各種問題。這類電源供應器的雜訊通常會與其轉換器之切換行為息息相 關。切換式直流轉直流(dc/dc)轉換器之電壓雜訊在切換及振鈴 (ringing)頻率之際,會呈現出不同的特性。在此篇論文中,我們首先 提出一些解析的運算式,於切換頻率且考量具寄生現象之複合性解耦合結 構時,可供用以評估電壓漣波。本研究亦同時發展出一種具有階梯 (step)電壓源的等效 RLC電路模型(圖 27),用來表示(模型化)該 降壓式轉換器輸入端之切換波型的振鈴雜訊,如圖 28所示以揭露模型之 測試板於相位節點模擬的電壓振鈴雜訊與實際量測之比較,其中該測試板 (含小型電感插入)用來驗證模型化電壓振鈴雜訊,由兩者電壓振鈴雜訊 波形圖之比較結果,可見彼此的峰值電壓及頻率關聯性極為接近。電路元 件佈置(layout)的被動寄生現象經由電路板之電磁模組量測取得。植基 於所提出模型的分析,新穎的設計方法可用以減輕電壓源之雜訊。其所揭 露之解析運算式及模型,已在一個高速系統之降壓式轉換器設計上經由量 測獲得驗證。透過降壓式轉換器設計及揭露模型之電路元件佈置 (layout)上應用最佳化的技術後,系統的效能已獲得改善。

圖 27:具有階梯(step)電壓源的等效 RLC電路模型

圖 28:以揭露模型之測試板於相位節點模擬的電壓振鈴 雜訊與實際量測之比較

### 12.A High-Performance CW Mobile Channel Sounder (一種高效能的連續波(CW)移動式頻道測深器(sounder))

作者群: Robert Johnk, Chriss Hammerschmidt, Irena Stange, Institute for Telecommunication Sciences (NTIA/ITS), U.S. Department of Commerce Boulder Laboratories, Boulder, Colorado 80205, USA

#### 摘要:

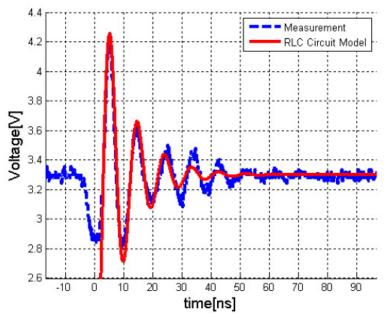

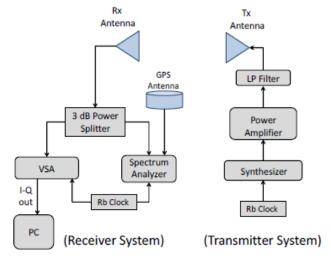

在此篇論述一種進階的移動式頻道測深器系統,此系統自從2010年以來, 已由美國國家電信暨資訊管理局(NTIA)所屬電信科學研究所的工程師們 研發中。本研究提出一些頻道測深器及重要系統元件之相關說明。接著, 我們亦闡明使用上述系統獲得各種量測及處理的無線電(radio)傳播結 果,藉以強調此系統本身擁有的適應機制及能力。此系統已被部署在許多 室外及室內傳播量測的實際案例,而且也使用於大樓內及大樓的穿透量 測。我們已述及一種電信科學研究所(ITS)研發出具有優秀效能特性的 連續波(CW)頻道測深器,如圖 29所示系統結構包含發射(Tx)及接收(Rx) 系統,其中發射系統端含合成器及功率放大器,而接收系統端將接收訊號 經由3分貝功率分波器(splitter)分送到頻譜分析儀及向量信號方析儀 (VSA),此VSA轉換訊號成為分離式基頻時間串列的同相及正交 (quadrature)複合性採樣訊號,供後端電腦處理及分析。此系統經過訊 號的處理及分析並能夠取得一些傳播參數(例如:路徑損失、快速衰減 (fading)特性、萊斯(連續機率分佈) K因子、基頻都卜勒(Doppler)功率 頻譜)(如圖 30所示訊號處理之流程圖),自2011年以來,亦被部署在 一些實際的量測案例。我們目前正透過提昇地理位置判定geolocation) 的能力及動態範圍以嘗試改善此系統之特性及功能,並將繼續使用此系統 量測可靠的數據,以利提供未來美國國家頻譜政策制定的參考。

圖 29: ITS研發的連續波(CW)頻道測深器

圖 30: 頻道測深器執行訊號處理之流程圖

# 13. Wideband Characterization of LCD Baseband Noise Modulation for RF Interference in Mobile Phones (行動電話關於LCD基頻雜訊調變引起之射頻(RF)干擾的寬頻特性化)

- 作者群:(1) Chulsoon Hwang, EMC Laboratory, Missouri University of Science and Technology, 4000 Enterprise Drive, Rolla, MO 65401, USA

- (2) Takashi Enomoto, 2Sony Global Manufacturing and Operations Corporation, 1-7-1 Konan Minato-Ku,

#### 摘要:

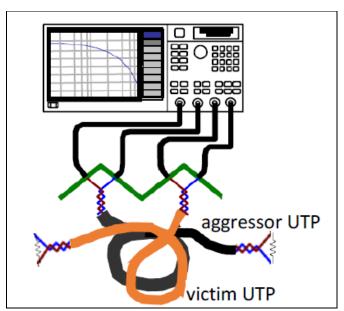

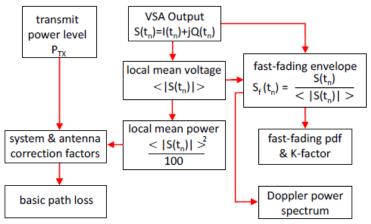

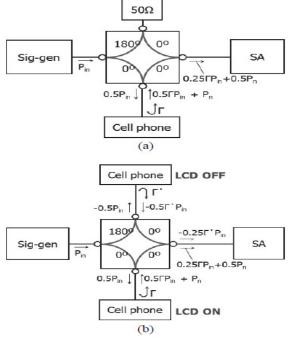

本篇論文提出一種可將射頻(RF)干擾特性化之寬頻量測技術,其中該射頻干擾係由液晶顯示器(LCD)基頻雜訊調變所引起的。於基頻帶頻率的範圍內,經由蜂巢式通訊之發射(Tx)載波訊號調變的液晶顯示器雜訊會干擾接收(Rx)訊號,此情形將導致射頻接收器之靈敏度降低問題。因為發射訊號與接升訊號頻段之間的頻率補償小(幾 + MHz而已),一種高發射訊號之帶拒頻段(band-rejection)濾波器顯現其重要性,在小的頻率補償伴隨強的發射載波訊號時,得以特性化相對小的調變雜訊。一般典型的解決方案即為使用一種收發雙工器(duplexer),此乃因為該收發雙工器僅被使用於專屬的通訊頻帶 - 尤指窄頻帶。

所揭露的量測技術運用一種 180°混合耦合器(hybrid coupler)及反射 消除方法(如圖 31所示以180°混合耦合器為基礎的架構:連接50Ω終端負 載以防止反射;使用虛擬DUT(待測物,此為手機)取代50Ω終端負載於反射 消除法),能夠獲得高發射訊號的帶拒頻段而毋需搭配任何頻率限制性的 元件。因此依據上述量測技術,對於液晶顯示器基頻雜訊的量測結果,可 從圖 32所示有無運用反射消除方法之頻譜差異比較。除此以外,該另一 種反射消除方法亦在此被提出且使用於較大的頻率補償案例。上述量測技 術有助於寬頻量測時,促使信號產生器與頻譜分析儀(SA)之間的隔離性 提高,且該量測技術可被用於寬頻帶頻率以特性化調變行為,不用針對個 別頻帶更換元件。

圖 31:以180°混合耦合器為基礎的架構:(a)50Ω 終端負載;(b)使用虛擬DUT於反射消除法

圖 32:LCD基頻雜訊之頻譜:(a)無運用反射消除法 ;(b)運用反射消除法

#### 肆、 心得及建議

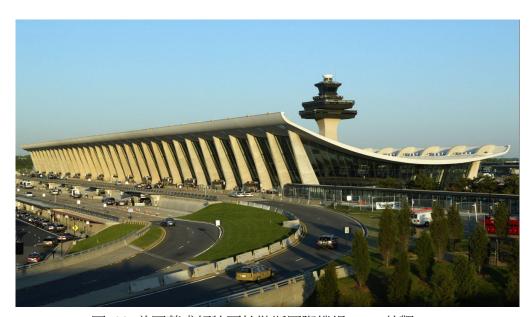

一、本次行程於 8 月 7 日清晨抵達及 8 月 12 日準備返國搭機所在的華盛頓特區 杜勒斯國際機場(IAD)(Washington Dulles International Airport)(如 圖 33)其實位於美國維吉尼亞州,得名於美國國務卿約翰·福斯特·杜勒斯, 主要航站由芬蘭裔美國建築師埃羅·沙里寧設計,主要服務於美國華盛頓哥倫 比亞特區和巴爾的摩,它也是美國聯合航空公司的主要樞紐站,機場占地面 積 47.9平方公里,每年旅客超過 2300萬人次,與全球 125 個機場有航線。 此外,位於台灣的桃園國際機場第一航廈乃仿造華府杜勒斯機場的設計,更 隨著當初國內桃園機場的落成而影響了後來新加坡樟宜機場的設計。

圖 33:美國華盛頓特區杜勒斯國際機場(IAD)外觀

華盛頓特區主要有 3 個機場,一個是華盛頓雷根國內機場,一個是華盛頓杜勒斯國際機場(IAD),另一個機場是巴爾的摩華盛頓國際機場(Baltimore Washington International Airport(BWI))。該華盛頓杜勒斯國際機場算是比較接近華盛頓特區的國際機場,但仍位於華盛頓特區之西邊大約相距 40Km(25 英里)遠的路程,該機場包括中央航站與 3 個機場大廳(以 A、B、C 及 D等 4 個航廈來區分),A 與 B 航廈連在一起,C 與 D 航廈連在一起,然而 A

- 與 B 航廈的登機門幾乎都屬於聯合航空的使用範圍,其他航空則分別位於 C 與 D 航廈, A、B 航廈與 C、D 航廈並不相通,但有 Mobil Lounge 的特殊接駁 巴士穿梭期間載運跨航廈的遊客。

- 二、IEEE P730 計畫規劃高速連接之電氣特性標準,並成立三個工作小組將治具的設計準則、去嵌入方法之驗證以及射頻參數品質之檢查寫成標準草案,已於去(2016)年底提出草案內容,此標準將有助於高頻連接系統之品質,減少因治具所造成的不確定度及錯誤解讀。

- 三、電磁資訊安全議題關係著智慧電網甚至 IoT (物聯網)的發展,高明的網路 駭客甚至可以利用電磁場探棒偵測未經過加密的電路所洩漏之電磁波,進行 資料的逆向工程(reverse engineering),因此相關的資安標準仍然一直相當受 到電磁國際標準組織的重視。

- 四、關於汽車電磁相容標準方面,CISPR 12 內容更新電動車上車用充電器的裝設規定,以及未來可能增加戶外試驗場(OTS)之驗證程序及關連性; CISPR 25 則更新附錄 I 的高電壓模組測試方法以及附錄 J 的 ESA ALSE 抗擾度驗證程序,已於去(2016)年底出版;而目前正在發展的新標準有輻射頻段小於 30 MHz 的 CISPR 36,預定在 2018年底出版。

- 五、IEC目前受關注的議題仍包含低頻電磁相容量測標準,此項標準目前由 CISPR子委員會 SC77A的第8工作小組負責相關標準的制定,涵蓋的頻段為 9kHz至150kHz,內容為制定與電網聯接變頻器之總電源輻射限制值以及安 裝於總電源上通訊裝置的抗擾度,此標準對於智慧電表之通訊相當重要。目 前委員會對於2至30kHz已有初步共識,然而在30至150kHz的非意圖式 輻射上尚未達成共識。

- 六、關於智慧電網部分,最新的 IEC 標準為發電站與變電站環境所要求的電磁抗 擾度通用標準(IEC 61000-6-5 Ed. 1.0:2015),此份標準主要提供發電站以及 高/中壓變電站(HV/MV substations)使用設備的電磁抗擾度參考,取代舊版 (2001年)的技術規範,並融入最新的 61000-2-5 環境相關內容。而智慧電網 互通性委員會(SGIP),目前正致力於智慧產業迫切需求的開放場域訊息匯流

(OpenFMB)計畫、加強網路安全以及互通性標準測試平台之發展。其中 OpenFMB 計畫並與工業物聯網聯盟(IIC)合作,應用標準化及無專利的網路 通信架構,以提供電力系統場域裝置之需求規範,該計畫也刻正由美國能源 部下的國家再生能源實驗室(National Renewable Energy Laboratory, NREL)與 其他合作夥伴進行試辦,找出可將業界各自不同的再生能源技術與電網整合 的方法,解決諸如當雲朵飄過屋頂上的太陽光電系統時,如何讓太陽能板 的變流器、太陽能電池以及電網端的電壓調節器能同步反應的互通性問 題,簡而言之,該計畫企圖讓發電業者選用 A 供應商的電池系統,選擇 B 供應商的太陽光電模組,再使用 OpenFMB 輕易地將兩種不同廠商所開發的系統進行整合。

- 七、專題演講的 Mr. Julies Knapp 指出了在相同頻寬下多系統的共存和互通性等問題,以及有意圖與非意圖等複合式電磁干擾問題皆使電磁相容扮演更重要且關鍵性的角色;而隨著處理器時脈的增加以及電路體積的縮小,未來將持續面臨信號完整性、電源完整性以及電磁相容的挑戰。

- 八、(一)第3天(8月9日)下午有關一系列「EMC FOR IoT」(物聯網設計之電磁相容性)專題研討會(Workshop)課程,其中包含一場由Frank Leferink(University of Twente, Enschede and Thales Netherlands)主講的Vulnerability of Wireless Systems to (Intentional)EMI(無線系統產生意圖性EMI之脆弱性(缺陷)),會中探討著當代社會非常地依靠一套能夠提供生活安全及品質的關鍵性公共基礎設施(CI),電子系統控制著大部分CI有關安全上關鍵性的運作,然而這些電子系統容易遭受電磁干擾(EMI),對於公共基礎設施造成的威脅可能來自敵人、恐怖份子、惡作劇或搞破壞之駭客,企圖以電磁(EM)波源干擾或破壞設施的運作,此種情形即被定義為意圖性電磁干擾(IEMI)。現今的無線通訊正普及於全世界,且社會依賴無線網路的程度亦正在成長中。通訊對於緊急服務的安全及有效運作,以及民眾的安全方面擔任重要的角色,對無線系統脆弱性的詳細探討,應清楚認知適當的防護策略及反制對策以期提高CI的強固性。在此,

- 我們可大致理解的缺陷分析,可歸納包含如下三種不同的干擾機制 (mechanism),而有不同因應的防護技術及策略,植基於頻域/時域/ 波形/空間域(Spatial domain)之 EM 多樣性(diversity):

- 1.接收器之實體損壞(damage):防護策略應考量頻帶內的限制器 (limiter)、考量前端濾波器抑制頻帶外(OOB)的干擾;

- 2.接收器之飽和(saturation)與阻斷(blocking):較強的干擾可能促使接收器飽和產生阻斷效應,此阻斷效應包括非線性影響(如諧波失真及交互調變)及靈敏度降低(Desensitization)(例如:增益壓縮及雜訊指數(noise figure)增加),防護策略則應考量使用具陡尖(sharp)聲頻(AF)濾波器之超外差(super-heterodyne)接收器及使用較高動態範圍之接收器;

- 3. (人為)干擾(jamming):可粗略分為射頻(RF)干擾及智慧型(intelligent)干擾,其中射頻干擾會降低訊號雜訊比(SNR)及增加誤碼率(BER),而智慧型干擾會降低偵測機率、產生虛假目標訊號、偽裝成 GPS 衛星傳送誤導的位置訊號,防護策略則以降低干擾信號比(JSR)為目標,應考量使用智慧型(smart)天線、展頻技術、高選擇性(selectivity)、強化編碼(coding)及交錯技術(interleaving)、更強健的通訊協定。

- (二)大會在第 3 天 (8 月 9 日)下午安排長達 4 小時有關一系列「EMC FOR IoT」(物聯網設計之電磁相容性)專題研討會(Workshop)課程中,與會者瞭解到很多連網裝置設計在承受外部 EMI 方面之實際上做得不夠,可能是成本、功率以及尺寸等因素帶來的壓力,讓某些廠商銷售的產品只能剛好達到最低程度要求,而問題就會來自那些連網裝置的意圖發射器(intentional radiators)。在某些情況下,「不良」發射器會發射過多的頻外(out of band)能量;相反的,有些接收器排除頻外能量的過濾能力有限或者根本就是缺乏這種能力。歐盟的無線電設備指令(European Radio Equipment directive)規定:「因無線電通訊或

是無線電定位目的,有意圖發射或接受無線電波的設備,對無線電頻譜 有系統性的使用;為了確保對無線電頻譜的有效利用,以避免有害的干 擾,所有這類設備都屬於本指令的適用範圍。」

針對上述提到的「避免有害干擾」,很多產品會在驗證實驗室接受EMI耐受度(immunity)測試,確保能符合歐盟指令以及其他適用標準,其他連網裝置也會進行自我認證,其中有些產品可能因為來自發射器的過量或鄰近頻道功率過量,或是採用不合格收發器,而無法通過合格測試。值得注意的是,Wi-Fi 乃使用未授權之2.4GHz頻段,涵蓋 2500~2690 MHz,而航空無線電導航以及無線電定位頻段係從 2700MHz開始,兩者之間只有100MHz的頻段差距,有些廉價無線裝置的功率就可能會溢過該間隙至鄰近GPS頻道造成GPS收發器功能之干擾。所以欲確保裝置與系統不會引起相互干擾的代價,正是功耗、尺寸以及成本的割捨及考量,譬如有些工程師想要拿掉濾波器,有些軟體定義無線電(SDR,係基於一款通用硬體平台來進行信號處理框架功能的軟體化處理)設計者完全不使用濾波器,認為只要靠軟體就能消除EMI問題,雖然 SDR具有支持多標準以及智能化頻譜利用等重新編程設定的能力,實際應用中卻仍受到軟、硬體工藝或者處理能力的限制。另所述及採用濾波器之紹外差

(super-heterodyne)接收器的效果最好,不過這種裝置的成本較高而且 耗電,因此許多裝置會考量使用較便宜、耗電較低的外差(heterodyne) 接收器。然而因為外差接收器比較敏感,與超外差接收器比較下,對於 來自電子干擾器(Jammer)的干擾耐受程度可能較差。除了軍方,使用電 子干擾器是不合法的,但還是可以在中國大陸深圳花500美元即可買得 到,可能會有歹徒意圖使用電子干擾器破壞家用或汽車保全系統,衍生 入侵住宅竊盜或是偷走車輛等問題。